**PRODUCT/PROCESS** CHANGE NOTIFICATION

PCN AMS/18/10425

# Analog, MEMS & Sensors Group (AMS)

Introduction of a new design for BlueNRG-1 products

### WHAT:

Progressing on the activities related to quality continuous improvement, ST is glad to announce a new design for BLUENRG1 family to correct some bugs reported on the product.

| Material              | Current process | Modified process                      | Comment                                       |

|-----------------------|-----------------|---------------------------------------|-----------------------------------------------|

| Register Die Id       | return 0x111    | return 0x113                          | traceability                                  |

| BOR operating voltage | down to 2.1V    | down to 1.7V                          | To prevent flash corruption at low<br>voltage |

|                       |                 | - Fix on SWD interface.               |                                               |

|                       |                 | -Minor functional fixes on<br>AUXADC. |                                               |

| Other modifications   |                 | Other minor changes to                |                                               |

|                       |                 | improve the ST                        |                                               |

|                       |                 | manufacturing FT yield.               |                                               |

|                       |                 | Modification of datasheet and         |                                               |

|                       |                 | errata sheet                          |                                               |

### WHY:

This change will contribute to improve product functionality and improve robustness.

#### HOW:

The qualification program consists mainly of comparative electrical characterization. You will find here after the qualification test plan which summarizes the various test methods and conditions that ST uses for this qualification program.

#### WHEN:

The new design will be implemented in April 2019.

### Marking and traceability:

Unless otherwise stated by customer's specific requirement, the traceability of the parts assembled with the new material set will be ensured by new internal sales type, date code and lot number.

The changes here reported will not affect negatively the electrical, dimensional and thermal parameters keeping unchanged all the information reported on the relevant datasheets. There is also no change in the packing process or in the standard delivery quantities.

Shipments may start earlier with the customer's written agreement.

# **Evaluation Report**

Standard Consumer Grade Qualification **F157 BLUENRG-134** F157 BLUENRG-132

| General lı                 | nformation             |

|----------------------------|------------------------|

| Product Line               | F157                   |

| Dreduct Deceription        | Bluetooth Low Energy   |

| Product Description        | Wireless Processor     |

| P/N                        | BLUENRG-134            |

| Product Group              | AMG                    |

| Product division           | General purpose analog |

| Package                    | VFQFPN 5x5x0.9 32L-    |

| Silicon Process technology | C090LP+flash           |

|                            |                        |

|                            |                        |

| Locations              |                  |  |  |  |  |  |  |

|------------------------|------------------|--|--|--|--|--|--|

| Wafer fab              | TSMC Fab14       |  |  |  |  |  |  |

|                        |                  |  |  |  |  |  |  |

| Assembly plant         | SUBCO ATP3, UTAC |  |  |  |  |  |  |

|                        | Thai             |  |  |  |  |  |  |

|                        |                  |  |  |  |  |  |  |

| Reliability Lab        | Grenoble GRAL    |  |  |  |  |  |  |

| Baliability accomment  | Paga             |  |  |  |  |  |  |

| Reliability assessment | Pass             |  |  |  |  |  |  |

|                        |                  |  |  |  |  |  |  |

## **PRODUCTS LIST**

| Product line P/N |             | Package         | Assy Plant |  |  |

|------------------|-------------|-----------------|------------|--|--|

| <b>E457</b>      | BLUENRG-134 | Wafer level CSP | Subco ATT  |  |  |

| F157             | BLUENRG-132 | VFQFPN 5x5 32L  | UTAC Thai  |  |  |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods. This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general

terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

## TABLE OF CONTENTS

| 1 | APPLICABLE AND REFERENCE DOCUMENTS | 5 |

|---|------------------------------------|---|

| 2 | GLOSSARY                           | 5 |

|   | RELIABILITY EVALUATION OVERVIEW    | 5 |

|   | 3.1 OBJECTIVES                     | 5 |

|   | 3.2 CONCLUSION                     | 5 |

| 4 | DEVICE CHARACTERISTICS             | 6 |

|   | 4.1 DEVICE DESCRIPTION             | 6 |

|   | 4.2 CONSTRUCTION NOTE              | 7 |

| 5 | TESTS RESULTS SUMMARY              |   |

|   | 5.1 TEST VEHICLE                   |   |

|   | 5.2 TEST PLAN AND RESULTS SUMMARY  |   |

| 6 | ANNEXES                            | 9 |

|   | 6.1 DEVICE DETAILS                 | 9 |

# **1** APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                        |

|--------------------|----------------------------------------------------------|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits  |

| ADCS0061692        | Reliability Tests and Criteria for Product Qualification |

## 2 GLOSSARY

| DUT | Device Under Test     |

|-----|-----------------------|

| PCB | Printed Circuit Board |

| SS  | Sample Size           |

|     |                       |

## **<u>3 RELIABILITY EVALUATION OVERVIEW</u>**

## 3.1 **Objectives**

The Aim of this report is to present characterization trials performed to qualify the design change and remind reliability trials performed on F128 BlueNRG (MSQTR and MSCSP), F174 BlueNRG (232/234) and F157 BlueNRG (132/134) products in order to reach qualification. BlueNRG is a Bluetooth Low Energy Wireless Processor based on ARM Cortex M0 core.

## 3.2 Conclusion

All trials have been performed with good results on both versions.

F157 BlueNRG-134 and BlueNRG-132 products are qualified.

# 4 DEVICE CHARACTERISTICS

## 4.1 Device description

# 4.2 Construction note

| Line:                   | F128 BLUENRG 1mil                | F128 BLUENRG 0.8mil              | F128 BLUENRG CSP         | F157 BLUENRG-132            | F157 BLUENRG-134            | F174 BLUENRG-<br>232  | F174 BLUENRG-<br>234        |

|-------------------------|----------------------------------|----------------------------------|--------------------------|-----------------------------|-----------------------------|-----------------------|-----------------------------|

| Comm. Product:          | BLUENRGQTR                       | BLUENRGQTR                       | BLUENRG CSP              | BLUENRG-132                 | BLUENRG-134                 | BLUENRG-232           | BLUENRG-234                 |

| Package Type:           | VFQFPN 5.0x5.0x0.9 32L-          | VFQFPN 5.0x5.0x0.9 32L-          | Wafer level CSP pitch0.4 | VFQFPN 5X5X1.0 32L          | Wafer level CSP<br>pitch0.4 | VFQFPN 5X5X1.0<br>32L | Wafer level CSP<br>pitch0.4 |

| Die Size:               | 2600 x 2500 μm                   | 2600 x 2500 μm                   | 2660 x 2560 μm           | <mark>2710 x 2580 μm</mark> | <mark>2710 x 2580 μm</mark> | 2710 x 2580 μm        | 2710 x 2580 μm              |

| Diffusion Plant:        | TSMC Fab14                       | TSMC Fab14                       | TSMC Fab14               | TSMC Fab14                  | TSMC Fab14                  | TSMC Fab14            | TSMC Fab14                  |

| Assembly Site:          | SUBCO ATP3                       | SUBCO ATP3                       | SUBCO ATT1               | UTAC Thai                   | SUBCO ATT1                  | UTAC Thai             | SUBCO ATT1                  |

| Test Site:              | GRENOBLE                         | GRENOBLE                         | GRENOBLE                 | GRENOBLE                    | GRENOBLE                    | GRENOBLE              | GRENOBLE                    |

| Fab Process:            | CMOS90LP+Flash                   | CMOS90LP+Flash                   | CMOS90LP+Flash           | CMOS90LP+Flash              | CMOS90LP+Flash              | CMOS90LP+Flash        | CMOS90LP+Flash              |

| Passivation:            | PSG + NITRIDE                    | PSG + NITRIDE                    | PSG + NITRIDE            | PSG + NITRIDE               | PSG + NITRIDE               | PSG + NITRIDE         | PSG + NITRIDE               |

| Die backside:           | Raw silicon                      | Raw silicon                      | Raw silicon              | Raw silicon                 | Raw silicon                 | Raw silicon           | Raw silicon                 |

| Die Attach:             | Ablestick AMK-6                  | Ablestick AMK-6                  | NA                       | Henkel 8600                 | NA                          | Henkel 8600           | NA                          |

| Mold Compound:          | Sumitomo G700                    | Sumitomo G700                    | NA                       | SUMITOMO G700               | NA                          | SUMITOMO G700         | NA                          |

| Lead Frame:             | Copper                           | Copper                           | NA                       | Copper                      | NA                          | Copper                | NA                          |

| Lead Finish:            | NiPdAu                           | NiPdAu                           | Bump leadfree            | <mark>Sn</mark>             | Bump leadfree               | Sn                    | Bump leadfree               |

| Package Size and Pitch: | VFQFPN 5.0x5.0x0.9 32L-E<br>p0.5 | VFQFPN 5.0x5.0x0.9 32L-E<br>p0.5 | Wafer level CSP pitch0.4 | VFQFPN 5X5X1.0 32L          | Wafer level CSP<br>pitch0.4 | VFQFPN 5X5X1.0<br>32L | Wafer level CSP<br>pitch0.4 |

| Bond Wire:              | Gold 1MIL                        | Gold 0.8MIL                      | NA                       | Gold 0.8MIL                 | NA                          | Gold 0.8MIL           | NA                          |

# 5 TESTS RESULTS SUMMARY

# 5.1 Test vehicle

| Lot<br># | Process/ Package  | Product Line | Comments |

|----------|-------------------|--------------|----------|

| 1        | QFN32 5x5 1mil    | F128         |          |

| 2        | QFN32 5x5 1mil    | F128         |          |

| 3        | QFN32 5x5 0.8mil  | F128         |          |

| 4        | WLCSP pitch 0.4mm | F128         |          |

| 5        | WLCSP pitch 0.4mm | F128         |          |

| 6        | QFN32 5x5 0.8mil  | F157         |          |

| 7        | WLCSP pitch 0.4mm | F174         |          |

| 8        | QFN32 5x5 0.8mil  | F174         |          |

Detailed results in below chapter will refer to Lot #.

# 5.2 Test plan and results summary

#### Yield verification

Yield on the new design measured in line with ST standard.

Statistical report

|                  | EWS  | Final test | Comment |

|------------------|------|------------|---------|

| WLCSP (Cpk>1.33) | 100% | 99.1%      | Conform |

Reliability

| <b>T</b>  |                                                                                                                                             | 011-11                                                                 | 0                           |                 | <b>0</b> 1111  |        |              |              | Fa           | ilure/SS     |           |       |       | Note   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------|-----------------|----------------|--------|--------------|--------------|--------------|--------------|-----------|-------|-------|--------|

| Test      | PC                                                                                                                                          | Std ref.                                                               | Conditions                  | SS              | Steps          | Lot 1  | Lot 2        | Lot 3        | Lot4         | Lot5         | Lot6      | Lot7  | Lot8  |        |

| Die Orien | nted Tes                                                                                                                                    | sts                                                                    | -                           | -               | -              | -      | -            |              | -            | -            | -         | -     | -     |        |

|           |                                                                                                                                             | JESD22                                                                 |                             |                 | 168H           | 0/74   | 0/78         | 0/73         |              |              | 0/95      |       |       |        |

| HTOL      | Ν                                                                                                                                           | A-108                                                                  | Tj = 125°C, BIAS            |                 | 500H           | 0/73   | 0/78         | 0/73         |              |              | 0/95      |       |       |        |

|           |                                                                                                                                             |                                                                        |                             |                 | 1000H          | 0/73   | 0/78         | 0/73         |              |              |           | -     |       |        |

| HTSL      | N                                                                                                                                           | JESD22                                                                 | Ta = 150°C                  |                 | 168H<br>500H   | 0/80   | -            | -            | 0/78<br>0/78 | 0/78<br>0/78 | -         |       |       |        |

| HIGL      | IN                                                                                                                                          | A-103                                                                  | 1a = 150 C                  |                 | 1000H          | 0/80   | -            | -            | 0/78         | 0/78         | -         |       |       |        |

| ELFR      | Ν                                                                                                                                           | JESD74                                                                 | Tj = 125°C, BIAS            |                 | 100011         | -      | -            | 0/480        | 0/239        | 0/10         | -         |       |       |        |

|           |                                                                                                                                             | 020071                                                                 | 1 - 120 0, 0.10             |                 |                |        |              | 0/ 100       |              | age Orien    | ted Tests |       | 1     |        |

| PC        | PC JESD22<br>A-113<br>PC JESD22<br>A-113<br>MSL3: Bake 24H @ 125°C<br>Soak 192H @ Ta=30°C<br>RH=60%<br>Oven Reflow @ Tpeak=260°C<br>3 times |                                                                        |                             | Final           | Pass           | -      | Pass         | Pass         | Pass         | -            |           |       |       |        |

| AC        | Y                                                                                                                                           | JESD22                                                                 | Pa=2Atm / Ta=121°C          |                 | 96H            | -      | -            | *0/80        | *0/79        | *0/80        | -         |       |       | *UHAST |

|           |                                                                                                                                             | A-102                                                                  | 1 4-25 4117 14-121 0        |                 | 168H           | 0/78   | -            |              |              |              | -         |       |       | 010101 |

| TO        | JESD22                                                                                                                                      | T. 0500 I. 15000                                                       |                             | 100cy           | -              | -      | 0/80         | 0/70         | 0/76         | -            |           |       |       |        |

| TC Y      | A-104                                                                                                                                       | Ta = -65°C to 150°C                                                    |                             | 500cy<br>1000cy | 0/78<br>0/78   | -      | 0/80<br>0/80 | 0/70<br>0/70 | 0/76<br>0/76 | -            |           |       |       |        |

|           |                                                                                                                                             |                                                                        |                             |                 | 168H           | 0/76   | -            | -            | 0/70         | 0/70         | -         |       |       |        |

| THB       | Y                                                                                                                                           | JESD22                                                                 | Ta = 85°C, RH = 85%, BIAS   |                 | 500H           | 0/75   | -            | -            |              |              | -         |       |       |        |

|           |                                                                                                                                             | A-101                                                                  |                             |                 | 1000H          | 0/75   | -            | -            |              |              | -         |       |       |        |

|           |                                                                                                                                             |                                                                        |                             |                 |                |        |              |              | Other        | Tests        |           |       |       |        |

|           |                                                                                                                                             | ADCS<br>0060102                                                        | HBM                         |                 |                | ±3KV   | -            | -            | Pass         | -            |           | 2kV   | 2kV   |        |

| ESD       | N                                                                                                                                           | (JESD22-<br>A114)<br>ADCS<br>0060102<br>(ANSI/ESD<br>STM5.3.1)<br>ADCS | CDM                         |                 |                | ±1.5KV | -            | -            | 400V         |              |           | 1000V | 1000V |        |

|           |                                                                                                                                             | ADCS<br>0060102<br>(JESD22-<br>A115)                                   | ММ                          |                 |                | ±300V  | -            | -            | 160V         |              |           |       |       |        |

| LU        | Ν                                                                                                                                           | ADCS<br>0018695                                                        | Current Inj.<br>Overvoltage |                 | ±200mA<br>X1.5 | Pass   | -            | -            | Pass         |              |           | Pass  | Pass  |        |

# 6 ANNEXES

## 6.1 Device details

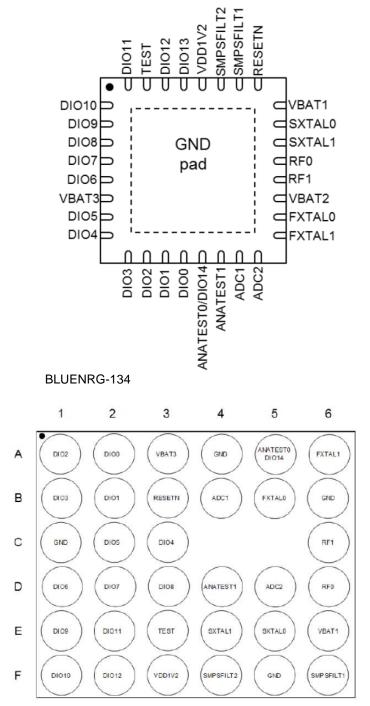

### 6.1.1 Pin connection

BUENRG-132

18-Dec-2018

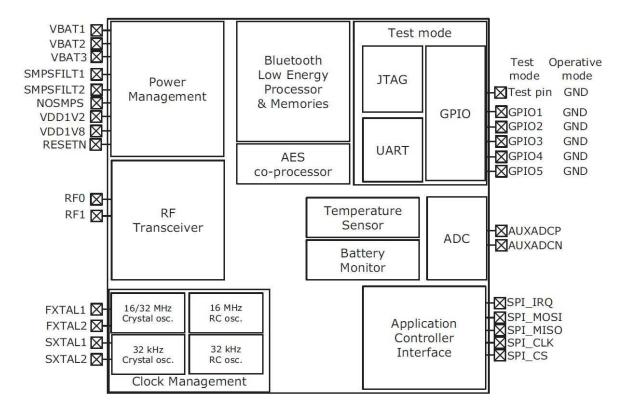

## **Block diagram**

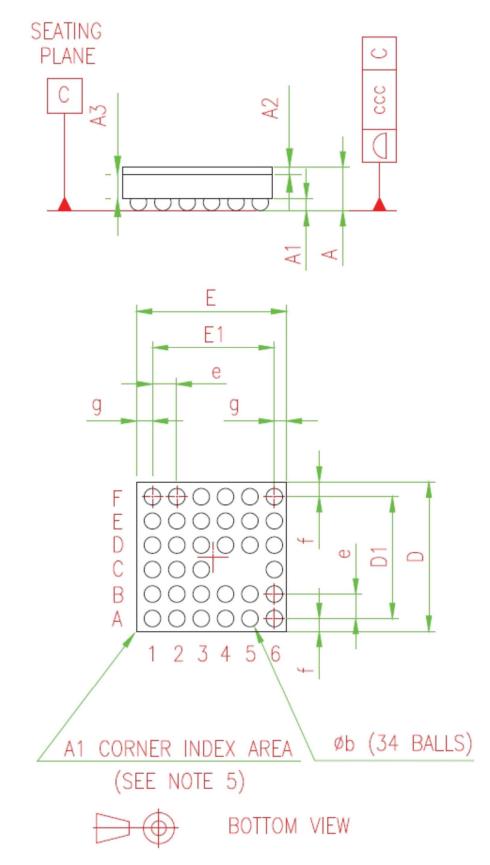

### 6.1.4 Package outline/Mechanical data

### TITLE: WLCSP 2.69x2.56x0.5 34 PITCH 0.4 BALL 0.25

### PACKAGE CODE: 01C1 (F157)

### JEDEC/EIAJ REFERENCE NUMBER: N/A

|      | DIMENSIONS |                  |       |       |                 |       |       |

|------|------------|------------------|-------|-------|-----------------|-------|-------|

|      |            | DATABOOK<br>(mm) |       |       | DRAWING<br>(mm) |       |       |

| REF. | MIN.       | TYP.             | MAX.  | MIN.  | TYP.            | MAX.  | NOTES |

| A    |            | 0.50             | 0.52  |       | 0.50            | 0.52  |       |

| A1   | 0.16       | 0.175            | 0.19  | 0.16  | 0.175           | 0.19  |       |

| A2   |            | 0.022            | 0.025 |       | 0.022           | 0.025 |       |

| A3   | 0.285      | 0.30             | 0.315 | 0.285 | 0.30            | 0.315 |       |

| b    |            | 0.27             |       |       | 0.27            |       | (2)   |

| D    | 2.50       | 2.56             | 2.58  | 2.50  | 2.56            | 2.58  | (3)   |

| D1   |            | 2.00             |       |       | 2.00            |       |       |

| E    | 2.63       | 2.69             | 2.71  | 2.63  | 2.69            | 2.71  | (4)   |

| E1   |            | 2.00             |       |       | 2.00            |       |       |

| e    |            | 0.40             |       |       | 0.40            |       |       |

| f    |            | 0.28             |       |       | 0.28            |       |       |

| g    |            | 0.35             |       |       | 0.35            |       |       |

| CCC  |            |                  | 0.05  |       |                 | 0.05  |       |

NOTES:

- (1) WLCSP stands for Wafer Level Chip Scale Package.

- (2) The typical ball diameter before mounting is 0.25mm.

- (3) D=f+D1+f.

- (4) E=g+E1+g.

- (5) The terminal A1 corner must be identified on the top surface by using a laser marking dot.

# **Tests Description**

| Test name                                         | Description                                                                                                                                                                                                                             | Purpose                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Oriented                                      | <u>.</u>                                                                                                                                                                                                                                | <u>.</u>                                                                                                                                                                                                                                                                                                                                                   |

| HTOL<br>Higt Temperature<br>Operating Life<br>HTB | The device is stressed in static or dynamic configuration, approaching the operative max. absolute ratings in terms of junction temperature and bias condition.                                                                         | To determine the effects of bias conditions and<br>temperature on solid state devices over time. It<br>simulates the devices' operating condition in an<br>accelerated way.<br>The typical failure modes are related to, silicon<br>degradation, wire-bonds degradation, oxide                                                                             |

| High Temperature<br>Bias                          |                                                                                                                                                                                                                                         | faults.                                                                                                                                                                                                                                                                                                                                                    |

| HTSL<br>High Temperature<br>Storage Life          |                                                                                                                                                                                                                                         | To investigate the failure mechanisms activated<br>by high temperature, typically wire-bonds solder<br>joint ageing, data retention faults, metal stress-<br>voiding.                                                                                                                                                                                      |

| ELFR<br>Early Life Failure<br>Rate                | The device is stressed in biased conditions at the max junction temperature.                                                                                                                                                            | To evaluate the defects inducing failure in early life.                                                                                                                                                                                                                                                                                                    |

| Package Oriented                                  |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                            |

| <b>PC</b><br>Preconditioning                      | The device is submitted to a typical temperature profile used for surface mounting devices, after a controlled moisture absorption.                                                                                                     | As stand-alone test: to investigate the moisture<br>sensitivity level.<br>As preconditioning before other reliability tests:<br>to verify that the surface mounting stress does<br>not impact on the subsequent reliability<br>performance.<br>The typical failure modes are "pop corn" effect<br>and delamination.                                        |

| AC<br>Auto Clave<br>(Pressure Pot)                | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                                                                                                                                | To investigate corrosion phenomena affecting<br>die or package materials, related to chemical<br>contamination and package hermeticity.                                                                                                                                                                                                                    |

| <b>TC</b><br>Temperature<br>Cycling               | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                                                                           | To investigate failure modes related to the<br>thermo-mechanical stress induced by the<br>different thermal expansion of the materials<br>interacting in the die-package system. Typical<br>failure modes are linked to metal displacement,<br>dielectric cracking, molding compound<br>delamination, wire-bonds failure, die-attach<br>layer degradation. |

| THB<br>Temperature<br>Humidity Bias               | The device is biased in static configuration<br>minimizing its internal power dissipation, and<br>stored at controlled conditions of ambient<br>temperature and relative humidity.                                                      | To evaluate the package moisture resistance<br>with electrical field applied, both electrolytic and<br>galvanic corrosion are put in evidence.                                                                                                                                                                                                             |

| Other                                             |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                            |

| ESD<br>Electro Static<br>Discharge                | The device is submitted to a high voltage<br>peak on all his pins simulating ESD stress<br>according to different simulation models.<br><b>CBM</b> : Charged Device Model<br><b>HBM</b> : Human Body Model<br><b>MM</b> : Machine Model | To classify the device according to his susceptibility to damage or degradation by exposure to electrostatic discharge.                                                                                                                                                                                                                                    |

| <b>LU</b><br>Latch-Up                             | The device is submitted to a direct current forced/sunk into the input/output pins. Removing the direct current no change in the supply current must be observed.                                                                       | To verify the presence of bulk parasitic effect inducing latch-up.                                                                                                                                                                                                                                                                                         |